# Compact Equivalent-Circuit Model for Snap-Back Phenomena in Ultra-Thin SOI MOSFET's and Practical Guideline for ESD-Protection Device Design

Yoichi SHIWAYA and Yasuhisa OMURA\*

(Received October 2, 2006)

#### **Abstract**

This paper proposes a compact equivalent-circuit model for the snap-back phenomenon in ultra-thin SOI MOSFET's. The model can be used in simulations of I/O circuits with ESD-protection devices. The model is more simple than past models, but it successfully reproduces the snap-back response. With the aid of many simulations, we propose a guideline for snap-back SOI MOSFET device design. Useful parameter-sensitivity equations for device characteristics are given for practical device designs.

**Key words**: SOI MOSFET, snap-back, parasitic bipolar action, electrostatic discharge, equivalent circuit model

#### 1. Introduction

Electrostatic discharge (ESD) phenomena continue to be an issue because of technology scaling, RF application requirements, and increasing customer expectations. Concurrently, ESD networks, technologies and device/circuit design practices are constantly undergoing both evolutionary and revolutionary changes<sup>1, 2)</sup>. The current levels of ESD events are generally in excess of 1 A for durations of from a few nanoseconds to 100 ns, and can severely damage integrated circuits. The most sensitive areas of integrated circuits are the devices directly connected to the bond pads. In order to protect the input/output (I/O) buffers from ESD stress, protection circuits that act as voltage clamps and current shunts are placed in parallel with the I/O circuits. An ESD protection circuit should turn on during the ESD event and clamp the excess voltage before the I/O buffer is damaged or worn out. In other words, engineers must predict the possibility of ESD damage in protection circuits and design robust device structures<sup>3, 4)</sup>.

The design and optimization of ESD protection circuits is greatly enhanced by the ability to perform circuit-level simulations of the protection circuits and the I/O buffers. Most available simulations do not reliably cover the high current region of circuit operation, but provide an approximate analysis of circuit behavior under ESD events<sup>5, 6)</sup>. The growing use of MOS-based protection circuits<sup>5, 7)</sup>, and the integration of protection circuits with internal circuitry<sup>6, 8)</sup>, has led to a need for simulations that are able to more accurately reproduce the behavior of a circuit under ESD events.

<sup>\*</sup>High-Technology Research Center, Kansai University, 3-3-35 Yamate-cho, Suita, Osaka, 564-8680 Japan

In this paper, we propose an equivalent circuit model for snap-back MOSFET's for ESD Protection circuits on silicon-on-insulator (SOI) substrates<sup>9, 10)</sup>. With the aid of a device simulator (*ISETCAD-DESISS*<sup>11)</sup>), the proposed equivalent circuit model is extensively examined by greatly varying many device parameters. Finally, we propose parameter-sensitivity equations that cover the gain of a parasitic bipolar transistor, the breakdown voltage (turn-on voltage), and the holding voltage, all of which are required in designing an effective device structure.

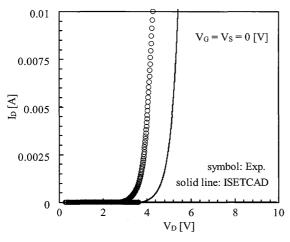

# 2. Experimental Results of Snap-back Operation

Before considering the equivalent circuit model, we examined the fundamental potential of the device simulator  $ISE-DESSIS^{11)}$ . Experimental results of snap-back operation in 50-nm-thick SOI MOSFET with 1- $\mu$ m-long channel are shown in Fig. 1; the channel length ( $L_{eff}$ ) is 0.8 $\mu$ m, the gate oxide layer thickness ( $t_{ox}$ ) is 7 nm, the SOI layer thickness ( $t_{si}$ ) is 50 nm, the buried oxide layer thickness ( $t_{BOX}$ ) is 80 nm, the p-type body-doping concentration ( $N_A$ ) is  $5 \times 10^{17} \text{cm}^3$ , and the n-type doping concentration of gate poly-Si and source/drain region is  $1 \times 10^{20} \text{cm}^3$ . Since the device works as a fully-depleted SOI MOSFET due to the positive fixed charges in the buried oxide layer, it does not exhibit snap-back operation at zero-substrate bias. Accordingly, we applied -10V to the substrate against the source terminal. We note that the breakdown voltage ( $V_{BD}$ ) is 3.6 V and holding voltage ( $V_{SB}$ ) is 2.9 V.

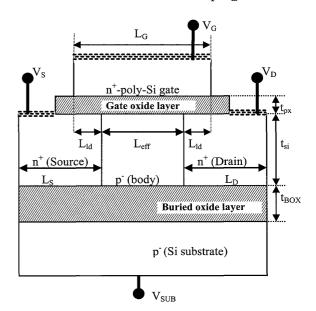

We also simulated the snap-back characteristic of an SOI MOSFET having device parameters identical to the actual device parameters, but no account of fixed charges in the buried oxide layer was taken: the fully-depleted operation does not occur. The device structure assumed here is shown in Fig. 2. It is assumed that the gate voltage ( $V_G$ ), the source voltage ( $V_S$ ), and the substrate voltage ( $V_{SUB}$ ) are all 0 V; the ramping rate of current applied to the drain terminal is 50 mA/ms; and the maximal voltage of 10 V is applied to the drain terminal because the holding voltage is about 4 V. Such a slow current ramping rate was

Fig.1 Snap-back operation of ultra-thin SOI MOSFET. Experimental result is shown with the simulation result (*ISE-DESSIS*). Substrate voltage ( $V_{sub}$ ) is -10 V in the experiment and 0 V in the simulation.

Fig. 2 Schematic of SOI MOSFET device structure simulated.

selected with a view to ease of measurement. However, the ramping rate is still fast compared to the measurement condition. When we assumed a slower ramping rate, the simulations took too long. Since the purpose of this simulation is to show the capability of *DESSIS*, we have shown only feasible simulation results in Fig. 1. We used the hydrodynamic transport model in device simulations, because a device experiencing snap-back has both high current and high heat flow. It is assumed that the carrier lifetime of electrons is  $10\,\mu$ s and that of holes is  $3\,\mu$ s. Here, we used the Masetti model<sup>12)</sup>, the Lombardi model<sup>13)</sup>, and the Canali model<sup>14)</sup> for carrier mobility models. We also assumed the Shockley-Read-Hall type lifetime model proposed by Fossum<sup>15)</sup>, the Auger recombination model described in<sup>11)</sup>, and the band-gap narrowing model <sup>16)</sup>. We can see that the simulation results broadly reproduce the experimental results. So, we can conclude the models implemented in the simulator are acceptable for practical use.

### 3. Device Structure and Device Parameters

In the following simulations, we also assumed the SOI MOSFET structure shown in Fig. 2. Basic device parameters are shown in Table I. It is assumed that the gate voltage ( $V_G$ ), the source voltage ( $V_S$ ) and the substrate voltage ( $V_{SUB}$ ) are all 0 V, and that the ramping rate of the current applied to the drain terminal is 5 mA/ns. It is also assumed that the maximal voltage of 12 V is applied to the drain terminal because the breakdown voltage (turn-on voltage) is about 7 V in *DESSIS* simulations. This rather rapid ramping rate was selected with a view to observing ESD events. We used the hydrodynamic transport model in device simulations because actual devices exhibit high currents with heat flow. In addition, we varied device parameters within the ranges shown in Table II. From the simulations, we derived three parameter-sensitivity equations for device design.

| OT 11 T   | ъ.    |         | and the second second |     |                      |

|-----------|-------|---------|-----------------------|-----|----------------------|

| Table I   | Basic | device  | parameters            | 1n  | simillations         |

| I ubic I. |       | ac vice | parameters            | *** | GIIII aia aia cioiio |

| Parameters                                       | Values [unit]                                           |

|--------------------------------------------------|---------------------------------------------------------|

| Channel length (L <sub>eff</sub> )               | 0.15 [ μ m]                                             |

| Gate width (W)                                   | 1.0 [ μ m]                                              |

| Gate oxide thickness (t <sub>ox</sub> )          | 3.5 [nm]                                                |

| SOI layer thickness (t <sub>si</sub> )           | 0.1 [ μ m]                                              |

| Buried oxide layer thickness (t <sub>BOX</sub> ) | 0.1 [ μ m]                                              |

| SOI doping conc. (N <sub>A</sub> )               | $9 \times 10^{17}  [\text{cm}^{-3}]$                    |

| Lateral diffusion length (L <sub>ld</sub> )      | 15 [nm]                                                 |

| Substrate doping conc. (N <sub>sub</sub> )       | $1 \times 10^{15}  [\text{cm}^{-3}]$                    |

| Source/Drain doping conc. (N <sub>S/D</sub> )    | $1 \times 10^{20}  [\mathrm{cm}^{-3}]$                  |

| Gate poly-Si doping conc. (N <sub>G</sub> )      | $1 \times 10^{20} \text{ [cm}^{-3}$ ]                   |

| Source/Drain length (L <sub>S/D</sub> )          | 0.555 [ μ m]                                            |

| Minority carrier lifetime                        | 10 (for electrons) [ $\mu$ s], 3 (for holes) [ $\mu$ s] |

Table II. Variable range of device parameters in simulations

| Parameters                                       | Values [unit]                                          |

|--------------------------------------------------|--------------------------------------------------------|

| Channel length (L <sub>eff</sub> )               | $0.07 - 0.27  [ \mu  \text{m}]$                        |

| Gate width (W)                                   | $0.1 - 10  [ \mu  \text{m}]$                           |

| Gate oxide thickness (t <sub>ox</sub> )          | 1.5 – 10 [nm]                                          |

| SOI layer thickness (t <sub>si</sub> )           | $0.1 - 0.5 [\mu m]$                                    |

| Buried oxide layer thickness (t <sub>BOX</sub> ) | $0.05 - 0.3  [ \mu  \text{m}]$                         |

| SOI doping conc. (N <sub>A</sub> )               | $2 \times 10^{17} - 5 \times 10^{18} \text{ [cm}^{-3}$ |

| Lateral diffusion length (L <sub>ld</sub> )      | 15-60 [nm]                                             |

| Source/Drain length (L <sub>S/D</sub> )          | $0.4 - 2.9 [\mu m]$                                    |

#### 4. Results and Discussion

## A. Equivalent circuit model

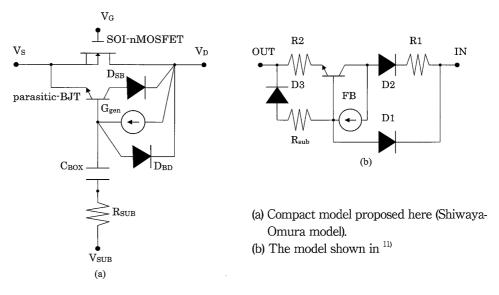

We investigated past equivalent circuit models<sup>17-21</sup>. Generally speaking, past models use many empirically-derived fitting parameters, which have no physical basis, depending on device parameters. For engineers, parameters for the equivalent circuit model should be actual physical parameters. Taking this as our guideline, we proposed the equivalent circuit model shown in Fig. 3(a). One of the past models is also shown in Fig. 3(b)<sup>20</sup> for comparison. We tried to minimize the number of circuit components, as follows: (i) parasitic resistances, such as R1 and R2 in Fig. 3(a), were removed and incorporated into the passive components of parasitic bipolar transistor; (ii) diode "D2 was replaced with " $D_{SB}$  in order to ensure the holding voltage ( $V_{SB}$ ) based on actual physical parameters; (iii) diode "D1 was replaced with " $D_{BD}$  to ensure the breakdown voltage based on actual physical parameters; and (iv) diode "D3 was removed and its role incorporated into the parasitic bipolar transistor.

Fig. 3 Equivalent circuit model for SPICE simulations.

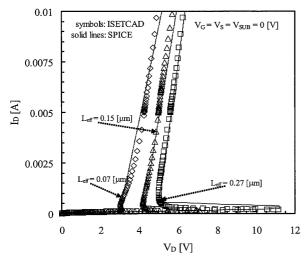

# B. Confirming the potential of the proposed model

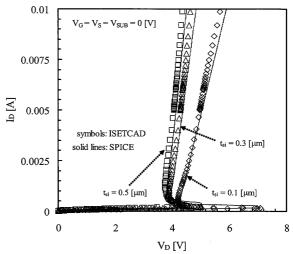

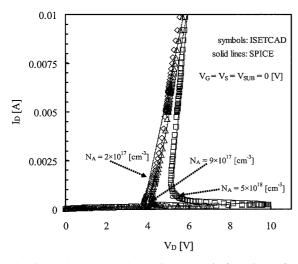

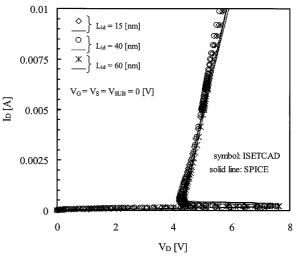

We assessed the potential of the proposed model (Fig. 3(a)). Typical simulation results are shown in Figs. 4 to 7, where circuit simulation results are compared to device simulation results. Fig. 4 shows the drain current dependence on drain voltage with the parameter of channel length ( $L_{eff}$ ); Fig. 5 shows the drain current dependence on drain voltage with the parameter of SOI layer thickness ( $t_{si}$ ); Fig. 6 shows the drain current dependence on drain voltage with the parameter of body-doping concentration ( $N_A$ ); and Fig. 7 shows the drain current dependence on drain voltage with the parameter of lateral diffusion length ( $L_{ld}$ ). Drain current dependence on drain current with the parameter of  $t_{BOX}$  or  $t_{ox}$  is not shown because the drain current is not so sensitive to them. Device simulation results are denoted by symbols, while circuit simulation results are denoted by solid lines. It is clear that the proposed model successfully reproduces the device simulation results.

# Compact Equivalent-Circuit Model for Snap-Back Phenomena in Ultra-Thin SOI MOSFET's and Practical Guideline for ESD-Protection Device Design

Fig. 4 Drain current dependence on drain voltage for various channel lengths  $(L_{eff})$ .

Fig. 5 Drain current dependence on drain voltage for various SOI layer thicknesses  $(t_{si})$

Fig. 6 Drain current dependence on drain voltage for various body-doping concentrations  $(N_A)$

Fig. 7 Drain current dependence on drain voltage for various lateral diffusion lengths  $(L_{td})$

# C. Parameter-sensitivity equations for practical device design

From the above simulation results, we derived several equations that can accurately express device characteristics, and so yield better designs. These equations can be used to design snap-back SOI MOSFET's for ESD protection circuits using the model shown in Fig. 3(a).

(i) Saturation current (IS) of diodes " $D_{SB}$  and " $D_{BD}$  is defined as

$$IS = A \frac{qD_n n_i^2}{L_{eff} N_A},\tag{1}$$

where A is the junction area, and the other parameters have the conventional meaning.

(ii) Constant current source  $(I_{gen})$  is defined with

$$I_{gen} = gain \cdot (I_{DS} + I_C) = (M-1) (I_{DS} + I_C),$$

(2)

where M is the avalanche multiplication factor,  $I_{DS}$  is the drain current of MOSFET, and  $I_C$  is

the collector current of parasitic bipolar transistor. Throughout the simulations, we assumed M=1.1 and "gain" for " $G_{gen}$  in Fig. 2(a) is 0.1.

(iii) Base resistance (RB) of parasitic bipolar transistor is defined as

$$RB \approx \rho \frac{(L_{eff} - 2x_d)}{T_{ci}W},\tag{3}$$

where  $x_d$  is the depletion layer width of the junction.

(iv) Substrate resistance ( $R_{SUB}$ ) is defined as

$$R_{SUB} = \rho \frac{(L_{eff} + L_D + I_S)}{t \cdot W}. \tag{4}$$

where t is the substrate thickness and  $\rho$  is the resistivity.

(v) Gain (BF) of parasitic bipolar transistor is defined as

$$BF = \beta_0 - \Delta \beta_{L_{eff}} \cdot L_{eff} - \Delta \beta_{L_{ld}} \cdot L_{ld} - \Delta \beta_{t_{si}} \cdot t_{si} - \Delta \beta_N \ln \left(\frac{N_A}{N_{ref}}\right), \tag{5}$$

where  $\beta_0$ ,  $\beta_{tsi}$ ,  $\beta_{Leff}$ ,  $\beta_{Lld}$ ,  $\beta_N$  and  $N_{ref}$  are constants independent of physical parameters.

(vi) Parameter-dependent shift value of the breakdown voltage ( $V_{BD}$ ) of SOI MOSFET is defined as

$$\Delta V_{BD} = \delta V_{BD 0} + \delta \varepsilon_{BDL_{eff}} \cdot L_{eff} + \delta \varepsilon_{BOL_{ld}} \cdot L_{ld} - \delta \varepsilon_{BDt_{si}} \cdot t_{si} - \delta \varepsilon_{BDt_{ox}} \cdot t_{ox} - \delta v_{BDN} \cdot \ln \left( \frac{N_A}{N_{ref}} \right), \quad (6)$$

where  $\delta V_{BD \ 0}$ ,  $\delta \varepsilon_{BDLeff}$ ,  $\delta \varepsilon_{BDLid}$ ,  $\delta \varepsilon_{BDtisi}$ ,  $\delta \varepsilon_{BDtox}$  and  $\delta v_{BDN}$  are constants independent of physical parameters.

(vii) Parameter-dependent shift value of the holding voltage ( $V_{SB}$ ) of SOI MOSFET is defined as

$$\Delta V_{SB} = \delta V_{SB\,0} + \delta \varepsilon_{SBL_{eff}} \cdot L_{eff} + \delta \varepsilon_{SBL_{ld}} \cdot L_{ld} - \delta \varepsilon_{SBt_{si}} \cdot t_{si} - \delta \varepsilon_{SBt_{ox}} \cdot t_{ox} - \delta v_{SBN} \cdot \ln\left(\frac{N_A}{N_{vol}}\right). \tag{7}$$

where  $\delta V_{SB~0}$ ,  $\delta \varepsilon_{SBLeff}$ ,  $\delta \varepsilon_{SBLid}$ ,  $\delta \varepsilon_{SBtoi}$ ,  $\delta \varepsilon_{SBtoi}$  and  $\delta v_{SBN}$  are constants independent of physical parameters.

Typical values of  $\beta_0$ ,  $\delta V_{BD\,0}$ ,  $\delta V_{SB\,0}$ , and the above constants are summarized in Table III. Since parameter values shown in Table III are not so sensitive to carrier lifetimes, we can adjust their values easily.

Table III. Constant values in simulations

| Parameters                                                                       | Values [unit]                             | Parameters                             | Values [unit]                         |

|----------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------|---------------------------------------|

| $\beta_0$                                                                        | 19                                        | $\delta  arepsilon_{BDtox}$            | $1.0 \times 106 \text{ [Vm}^{-1}$ ]   |

| $\Deltaeta_{\mathit{Leff}}$                                                      | $2.6 \times 10^7 \text{ [m}^{-1}\text{]}$ | $\delta v_{BDN}$                       | 0.04 [V]                              |

| $\Deltaeta_{{\scriptscriptstyle L}{\scriptscriptstyle l}{\scriptscriptstyle d}}$ | $3.0 \times 10^7  [\text{m}^{-1}]$        | $\delta V_{{\scriptscriptstyle SBO}}$  | 0.47 [V]                              |

| $\Deltaeta_{tsi}$                                                                | $0.7 \times 10^7 \text{ [m}^{-1}\text{]}$ | $\deltaarepsilon_{	ext{SBLeff}}$       | $3.2 \times 10^5  [\text{Vm}^{-1}]$   |

| $\Deltaoldsymbol{eta}_N$                                                         | 1.7                                       | $\delta  arepsilon_{	ext{	iny SBLId}}$ | $1.0 \times 10^6  [\mathrm{Vm}^{-1}]$ |

| $N_{\it ref}$                                                                    | $1 \times 10^{18} \text{ [cm}^{-3}$ ]     | $\deltaarepsilon_{\mathit{SBtsi}}$     | $7.3 \times 10^4  [\text{Vm}^{-1}]$   |

| $\delta V_{\scriptscriptstyle BD0}$                                              | 1.3 [V]                                   | $\deltaarepsilon_{	ext{SBtox}}$        | $2.0 \times 10^6  [\text{Vm}^{-1}]$   |

| $\deltaarepsilon_{	extit{BDLeff}}$                                               | $1.5 \times 10^5  [\mathrm{Vm}^{-1}]$     | $\delta v_{SBN}$                       | 0.02 [V]                              |

| $\deltaarepsilon_{	extit{BDLId}}$                                                | $1.6 \times 10^5  [\mathrm{Vm}^{-1}]$     | gain                                   | 0.1                                   |

| $\_$ $\deltaarepsilon_{\mathit{BDtsi}}$                                          | $2.2 \times 10^5  [\text{Vm}^{-1}]$       | _ M                                    | 1.1                                   |

#### 5. Conclusion

We proposed a compact equivalent-circuit model of the snap-back phenomenon in ultrathin SOI MOSFET's. The model can be used in circuit simulations of I/O circuits with ESD-protection devices. The model is simpler than past models, but it successfully reproduces the snap-back operation of ultra-thin SOI MOSFET's. With the aid of many simulations, we also proposed a guideline for snap-back SOI MOSFET device design. Useful parameter-sensitivity equations for device characteristics were also given for practical device designs.

#### References

- 1) A. Amerasekera and C. Duvvury, "ESD in Silicon Integrated Circuit," Wiley, New York (1995).

- 2) S. Ghandi, "Semiconductor Power Devices," Wiley, New York (1977).

- 3) S. H. Voldman, "State of the Art Electrostatic Discharge Protection: Physics, Technology, Circuits, Design, Simulation, and Scaling," *IEEE J. Solid-State Circuits*, vol. 34, pp. 1272-1282 (1999).

- 4) S. Wakita and Y. Omura, "Sub-circuit Models of Silicon-on-insulator Insulated-gate pn-junction Devices for Electrostatic Discharge Protection Circuit Design and their Applications," Solid-State Electronics, vol. 47, pp. 1943-1952 (2003).

- 5) C. Duvvury and C. Diaz, "Dynamic Gate-Coupled NMOS for Efficient Output ESD Protection," *Proc.* 30<sup>th</sup> IEEE Int. Reliability Physics Symp. (1992) pp. 141-150.

- 6) D. Krakauer and K. Mistry, "Circuit Interactions during ESD," *Proc.* 16<sup>th</sup> IEEE EOS/ESD Symp. (1994) pp. 113-119.

- 7) E. Worley, R. Gupta, B. Jones, R. Kjar, C. Nguyen and M. Tennyson, "Sub-Micron Chip ESD Protection Schemes which Avoid Avalanching Junctions," Proc. 17<sup>th</sup> IEEE EOS/ESD Symp. (1995) pp. 13-20.

- 8) S. Dabral, R. Aslett and T. Maloney, "Core Clamps for Low Voltage Technologies," *Proc.* 16 th IEEE EOS/ESD Symp. (1994) pp. 141-149.

- 9) J. Bielefield, G. Pelz, H. B. Abel and G. Zimmer, "Dynamic SPICE-Simulation of the Electrothermal Behavior of SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 42, pp. 1968-1974 (1995).

- 10) S. Voldman, F. Assaderaghi, J. Mandelman, L. Hsu and G. Shahidi, "Dynamic Threshold Body- and Gate-Coupled SOI ESD Protection Networks," *Proc.* 19<sup>th</sup> IEEE EOS/ESD Symp. (1997) pp. 210-220.

- 11) TCAD DESSIS, Operations Manual (ver. 7.0), Synopsys Inc.

- 12) G. Masetti, M. Severi and S. Solmi, "Modeling of Carrier Mobility against Carrier Concentration in Arsenic, Phosphorus, and Boron-doped Silicon," *IEEE Trans. Electron Devices*, vol. ED-30, pp. 764-769 (1983).

- 13) C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, "A Physically Based Mobility Model for Numerical Simulation of Nonplanar Devices," *IEEE Trans. Computer-Aided Design*, vol. 7, pp. 1164-1171 (1988).

- 14) C. Canali, G. Majini, R. Minder and G. Ottavini, "Electron and Hole Drift Velocity Measurements in Silicon and their Empirical Relation to Electric Field and Temperature," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 1054-1047 (1975).

- 15) J. G. Fossum and D. S. Lee, "A Physical Model for the Dependence of Carrier Lifetime on Doping Density in Nondegenerate Silicon," *Solid State Electron.*, vol. 25, pp. 7412-747 (1982).

- 16) J. W. Slotboom and H. C. de Graaff, "Bandgap Narrowing in Silicon Bipolar Transistors," IEEE

- Trans. Electron Devices, vol. ED-24, pp. 1123-1125 (1977).

- 17) M. Pinto-Guedes and P. C. Chan, "A Circuit Simulation Model for Bipolar-induced Breakdown in MOSFET," *IEEE Trans. Computer-Aided Design*, vol. 7, pp. 289-294 (1988).

- 18) C. H. Diaz, S.-M. Kang and C. Duvvury, "Circuit-Level Electrothermal Simulation of Electrical Overstress Failures in Advanced MOS I/O Protection Devices," *IEEE Trans. Computer-Aided Design*, vol. 13, pp. 482-493 (1994).

- 19) K. Sonoda, M. Tanizawa, K. Ishikawa, N. Kotani and T. Nishimura, "Circuit-Level Electrothermal Simulations of Electrostatic Discharge in Integrated Circuits," *IEICE Trans. Electron.*, vol. E83-C, pp. 1317-1322 (2000).

- 20) K. Ise, J. Mano, H. Ishizuka, K. Tsuneno and K. Okuyama, "Circuit-Level Simulations of ESD Prediction for Input Protection Circuits," *IEICE Trans. Electron.*, vol. J86-C, pp. 634-642 (2003) (in Japanese).

- 21) Y. Tosaka, H. Anzai, K. Suzuki and H. Oka, "New Scheme of Electrostatic Discharge Circuit Simulations Using Protection Device Model with Generated-Hole-Dependent Base Resistance," *Jpn. J. Appl. Phys.*, vol. 43, pp. 1673-1676 (2004).